"Precise Exception Semantics in Dynamic Compilation"

Michael Gschwind, Erik Altman IBM T.J. Watson Research Center

2002 Symposium on Compiler Construction

presented by nick black <nickblack@linux.com> for cs8803dc 2010-02-02

#### **Motivation**

- Synchronous exceptions are bound to instructions and cannot be deferred

- Expose user-managed state, violating Bruening's (2004) model of even extrinsic compatibility

- Hardware-signaled exceptions mark our PC, not guest's

- Optimization changes user-managed state (DCE, PRE, code sinking...)

"We're gonna need a bigger ROB." (actually, a side table)

# Difficulties of virtualizing exceptions:

- Determination of guest PC from host notifications (only applicable outside *interpretive trap detection*)

- Dynamic binary translation eliminates bijection!

- Avoid exponential state costs from optimizing

# Program Counter Discovery, Part 1/3

- Easy for interpretation. Either:

- Trap case is detected by the VM (interpretive detect), or

- Synchronous exception is delivered before PC update (or any other externally-visible changes)

- Either way, the source PC is directly available

# Program Counter Discovery, Part 2/3

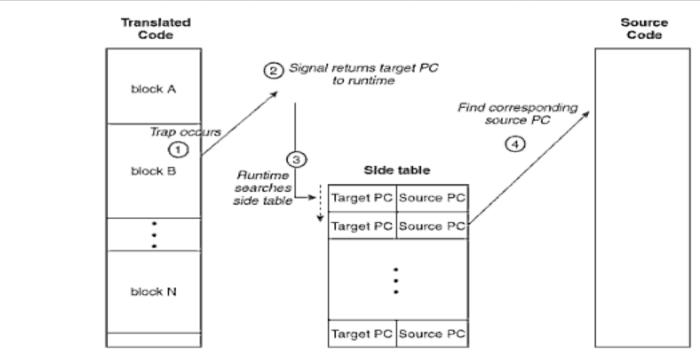

• Things become more difficult for binary translation!

Figure 3.21 Finding the Trapping Source PC, Given the Target PC. (1) The trap occurs and (2) the signal handler returns the target PC to the runtime software. The runtime (3) does a search of the side table (4) to find the corresponding source PC that caused the trap.

### Program Counter Discovery, Part 3/3

- Inefficiencies in Target PC / Source PC map:

- Pair of address pointers for each translated op (could be larger than translated source!)

- Given target op might correspond to multiple source ops

- Both can be addressed via translation block map

- Coalesce various instructions of a translation block

- Augment the translation block map with register maps

- See Figure 3.22 and Chapter 4 of the textbook

# Code Optimization with Precise Exceptions

Let us consider the following (contrived) code:

ADDPD %xmm0, %xmm1 MOVAPD 0x20(%ebx), %xmm1 ADDPD %xmm0, %xmm1

# SIMD add into xmm0 # aligned load into xmm1 # SIMD add into xmm0

- First add could be excised via dead code elimination

- ...unless there's a page fault at 0x20(%ebx)

#### Where else have we seen this issue?

Out-of-order processor

"Implementing Precise Interrupts in Pipelined Processors" James Smith and Andrew Pleszkun, IEEE ToC, 1988

- Since IBM 360/91, Tomasulo augmented via ROB: Reorder buffer feeds results Exceptions accounted for at ROB graduation

- Static compilation

- Reorganization of code around branches needs fixups

- Exponential state for static CFG amendments

- With access to source, dynamic compilers fixup just-in-time

### Low-Cost Recovery from Exceptions

- Retain information regarding modified operations

- Including preservation of input values

- Reconstruct state on the fly when (rarely) needed

- Is this infrequency assumption always valid? What if not?

- p. 197: "maintain [an unoptimized] translation to the side"

- Can't address architecture-invisible elements (intrinsic compatibility)

- Aside: suitable for static compilers?

- Superficial similarity to retaining debugging symbols

- More like running -g binary in a debugger (due to state)

- Method likely unfit for static compilation.

- So it goes.

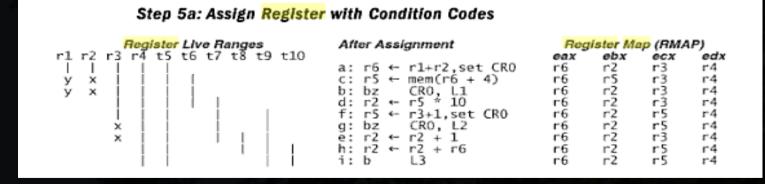

# A Scheduling Algorithm, Part 1/2 (ibid. §3.5.2)

"Out-of-Order Execution Tech. for RT Binary Translators" Bich Le, 8<sup>th</sup> Conference on ASPLOS, 1998

- Assume or force single-assign IR (SSA, CPS...)

- Derive the register map:

Reorder the code:

```

Before Scheduling

After Scheduling

a: t5 ← t0 + t1.set CRO

a: t5 ← r1 + r2,set CR0

CRO. L1

c: t6 ← men(t5 + 4)

CRO, L1

t5

← t6 * 10

t5

← t7 + 1

← r3 + 1.set CR0

f: t9

← t3 + 1,set CRO

CRO. L2

CRO, L2

← t7 + 1

+ t8 + t5

Compensation:

L2: t8 ← t7 + 1

```

### A Scheduling Algorithm, Part 2/2

Determine checkpoints:

```

Commit

Checkpoint

Register Map (RMAP)

After Scheduling

ebx

a: t5 ← r1 + r2,set CR0

r4

← mem(t5 + 4)

t5

b.c

← t6 ° 10

← r3 + 1.set CR0

t5

CRO. L2

t5

← t7 + 1

t10 ← t8 + t5

```

Assign registers, paying attention to flag register(s)

Add compensation code and run that sumbitch

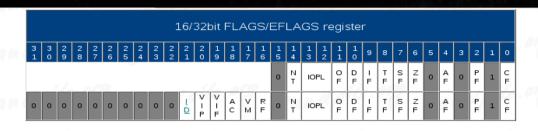

# **EFLAGS**

- Delicious!

- Lots of messy details

note: Do not rely on undefined integer FLAGS behavior.

| undefined integer FLAGS behavior |                                                                                                                                                                               |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------|--------|---------|----------|--------|-------------------------------|--------|----------|---------|----------|-----|---------|------|----|----------|------|--------|

| Instruction                      | P5 Core                                                                                                                                                                       |                                                                              |          |        |         |          |        | P6 Core <sup>#0</sup>         |        |          |         |          |     | P4 Core |      |    |          |      |        |

|                                  | OF                                                                                                                                                                            | SF                                                                           | ZF       | AF     | PF      | CF       | OF     | SF                            | ZF     | AF       | PF      | CF       | OF  | SF      | ZF   | AF | PF       | CF   | Case   |

| ААА                              | OF16                                                                                                                                                                          | SF16                                                                         | 2F16     | м      | PF      | Εм       | U      | 0                             | ZF16   | м        | PF      | м        | 0   | 0       | 25-8 | м  | PF       | -M   |        |

| AAS                              |                                                                                                                                                                               |                                                                              |          |        |         | 2.1      |        |                               |        |          | #1      | 100      |     |         |      |    |          | 1777 | 017    |

| AAM                              | 0                                                                                                                                                                             | М                                                                            | м        | 0      | М       | 0        | 0      | М                             | М      | 0        | М       | 0        | 0   | м       | М    | 0  | М        | 0    | V      |

| AAD<br>DAA                       | OF8                                                                                                                                                                           |                                                                              | <u> </u> | AF     |         | CF       | OFE    |                               | -      | AF       |         | CF       |     | _       | _    |    | <b>!</b> |      |        |

| DAS                              | OF8                                                                                                                                                                           | м                                                                            | м        | м      | M       | M        | U      | М                             | М      | м        | М.      | М        | 0   | м       | м    | м  | М        | М    | 000    |

| AND, OR, TEST, XOR               | 0                                                                                                                                                                             | М                                                                            | М        | 0      | М       | 0        | 0      | M                             | M      | 0        | М       | 0        | 0   | М       | М    | 0  | М        | 0    | 017    |

| (I)MUL                           | М                                                                                                                                                                             | U                                                                            | U        | U      | U       | М        | М      | U                             | U      | U        | U       | м        | М   | SF      | ZF   | 0  | PF       | М    | V      |

| (I)DIV                           | ?                                                                                                                                                                             | ?                                                                            | ?        | ?      | ?       | ?        | U      | U                             | U      | U        | U       | U        | U   | U       | U    | U  | U        | U    |        |

| F(U)COMI(P)                      | not supported                                                                                                                                                                 |                                                                              |          |        |         |          | 0      | 0                             | М      | 0        | М       | М        | 0   | 0       | М    | 0  | М        | М    | 1100   |

| BT, BTC, BTR, BTS                | #2                                                                                                                                                                            | U                                                                            | U        | U      | U       | М        | U      | U                             | U      | U        | U       | М        | U   | U       | U    | U  | U        | М    | 1      |

| BSF                              | 0                                                                                                                                                                             | 0                                                                            | 77       |        | 1       | 0        |        |                               |        |          |         |          |     |         | 100  |    | 1        |      | src=0  |

| BSF                              | ?                                                                                                                                                                             | ?                                                                            | м        | ?      | ?       | ?        | u      | U                             | м      | U        | U       | U        | 0   | 0       | м    | 0  | PF       | 0    | src<>0 |

| BSR                              | 0                                                                                                                                                                             | 0                                                                            | 101      | 1      | 1       | 0        | l l °  | ,                             |        |          |         |          |     |         |      |    | 1        | "    | src=0  |

| BSR                              | ?                                                                                                                                                                             | ?                                                                            | 00       | _      | ?       | ?        |        |                               | 9.00   |          |         |          |     |         | 00   |    | PF       |      | src<>0 |

| ROL and ROR                      | OF×                                                                                                                                                                           | U                                                                            | U        | U      | U       | М        | U      | U                             | U      | U        | U       | М        | #3  | U       | U    | U  | U        | М    | >1     |

| RCL and RCR                      | OF×                                                                                                                                                                           | U                                                                            | U        | U      | U       | М        | #4     | U                             | U      | U        | U       | М        | #3  | U       | U    | U  | U        | М    | >1     |

| SHL and SHR<br>SAL and SAR       | M                                                                                                                                                                             | М                                                                            | М        |        | M       | M        | М      | M                             | M      |          | M       | М        | М   | М       | М    |    | М        | М    | 1      |

| SAL and SAR                      | OF×                                                                                                                                                                           | М                                                                            | М        | 1      | М       | М        | U      | М                             | М      | U        | М       | М        | OF× | М       | М    | 0  | М        | М    | 2N     |

|                                  |                                                                                                                                                                               | М                                                                            | М        |        | М       | CF<br>#5 |        | М                             | М      |          | М       | CF<br>#6 |     | М       | М    |    | М        | CF   | >N     |

| SHLD and SHRD <sup>#7</sup>      | М                                                                                                                                                                             | М                                                                            | М        |        | М       | М        | М      | М                             | М      |          | М       | М        | М   | М       | М    |    | М        | М    | 1      |

|                                  | OF×                                                                                                                                                                           | М                                                                            | М        | 1      | М       | M        | U      | М                             | М      | U        | M       | М        | OF× | М       | М    | 0  | М        | М    | 2N     |

|                                  |                                                                                                                                                                               | SF                                                                           | ZF       |        | PF      | CF       |        | SF                            | ZF     |          | PF      | CF       |     | SF      | ZF   |    | PF       | CF   | >N     |

| Notes                            | Descriptions                                                                                                                                                                  |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #0                               | except for Pentium Pro: TEST (AF=U) this is considered an outlier which got fixed in the P2 except for Core 2: AAA (OF=1), AAS (OF=0), DAA (OF=0), DAS (OF=0) instead of OF=U |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #1                               | if (((AL & 0Fh) > 09h)   (AF = 1)) { PF[AL+06h] } else { PF[AL] }                                                                                                             |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #2                               | as if a ROR was performed, i.e. OFR                                                                                                                                           |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #3 U if size=0. else OFx         |                                                                                                                                                                               |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

|                                  | ROL/ROR size = (count & 1Fh)  RCL/RCR size = (count & 1Fh) % (N+1)                                                                                                            |                                                                              |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #4                               |                                                                                                                                                                               |                                                                              |          |        |         |          |        |                               |        |          | /       | +        | 019 |         |      |    |          | 110  | 019    |

| ***                              |                                                                                                                                                                               | U if dword, else U if size>1, else OFx  RCL/RCR size = (count & 1Fh) % (N+1) |          |        |         |          |        |                               |        |          |         |          |     |         |      |    |          |      |        |

| #5                               | ? for                                                                                                                                                                         | SHR/S                                                                        | HL/S/    | AL byt | e with  | count    | t=16 o | count                         | =24    |          |         |          |     |         |      |    |          |      |        |

| #6                               | for Si                                                                                                                                                                        | IR byt                                                                       | e: if (N | viSB[d | st] = : | L) & ((( | count  | & 1Fh)                        | % 8)   | = 0) { : | 1 } els | e { 0 }  |     |         |      |    |          |      |        |

| #7                               | P6 us                                                                                                                                                                         | es dst                                                                       | t:src:D  | ST fo  | r SHL   | D, and   | DST:   | src:dst<br>src:dst<br>src:dst | for SH | RD       | زم      | U.       | 9   |         | 50   | al | d p      | ile  | .019   |

(stolen from sandpile.org)

### **Other Optimizations**

- Code sinking

- Repair note inserted in original op slot

- No extra input value preservation necessary

- Unspeculation (PRE)

- DCE along redundant paths, code sinking where needed

- Constant propagation

- Constant folding

- Commoning

- Elimination of ISA-specific condition code updates

- Patch repair code into eliminated code via flag bit! (Mmm, I especially enjoyed that one)